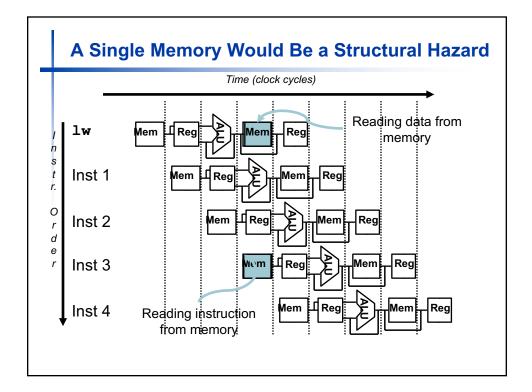

## **Structural Hazards**

- A structural hazard is a *conflict for use of a resource*.

- A combination instruction/data memory would create a structural hazard in a pipelined architecture

- Load/store requires data access.

- Instruction fetch would have to stall for that cycle.

- Fix with separate instruction and data memories (I\$ and D\$).

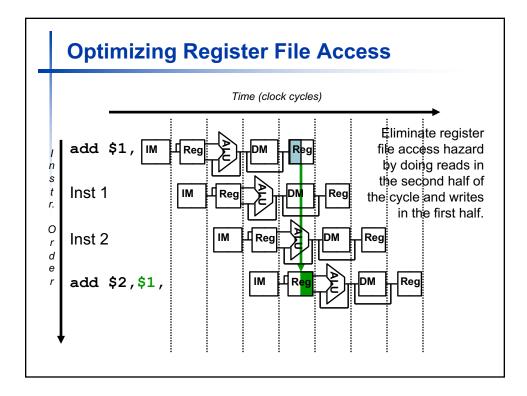

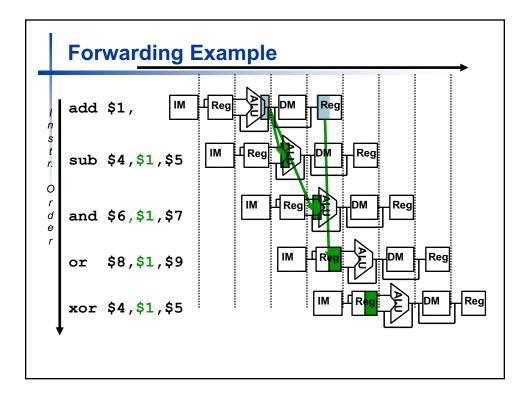

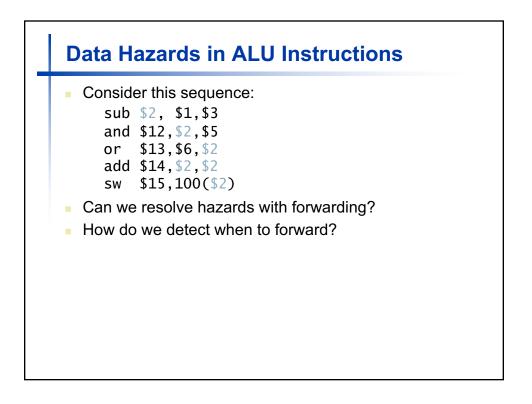

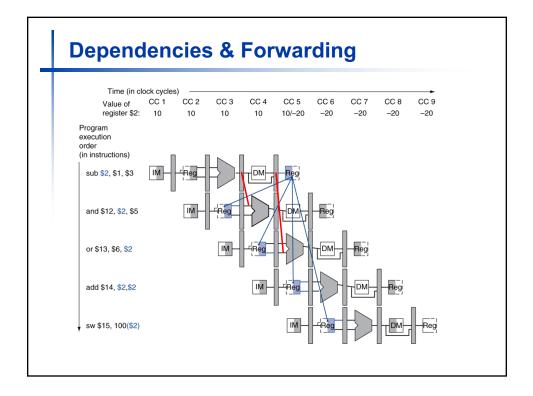

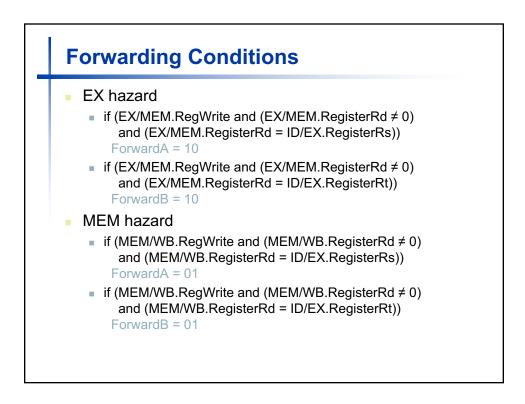

- Consider the sequence:

- add \$1,\$1,\$2 add \$1,\$1,\$3 add \$1,\$1,\$4

- Both hazard situations occur

- Want to use the most recent.

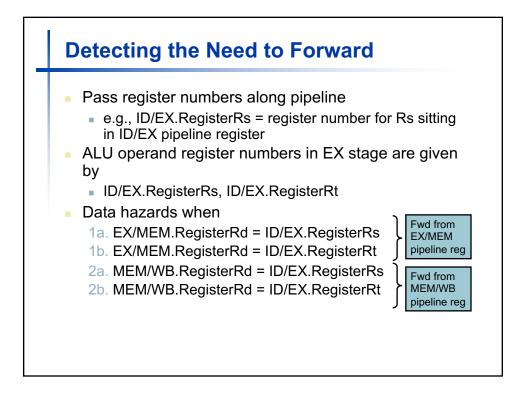

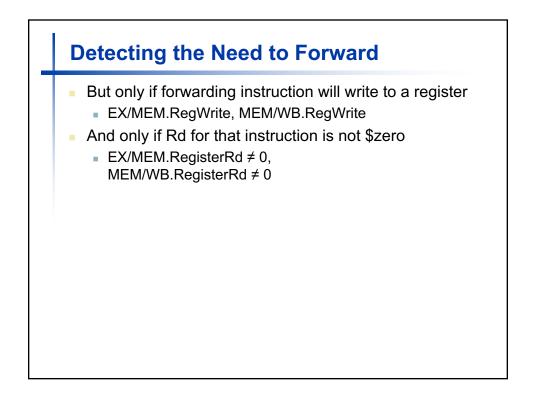

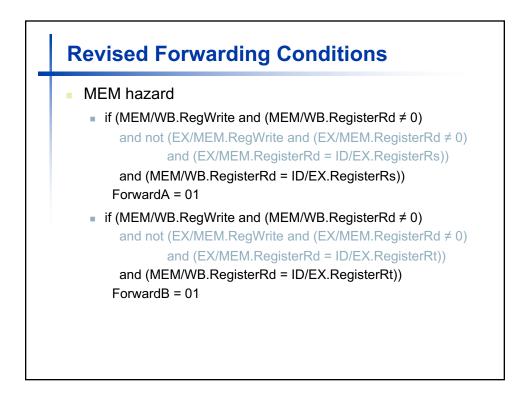

- Revise MEM hazard condition

- Only fwd if EX hazard condition isn't true.

## **Summary**

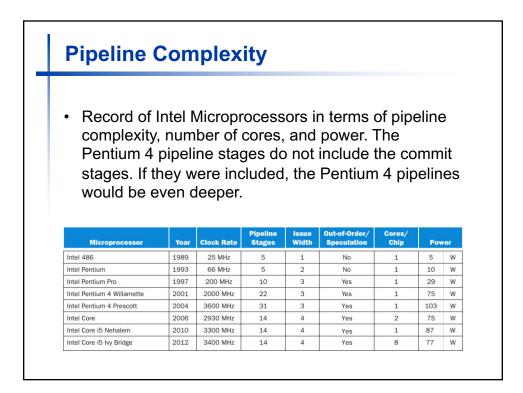

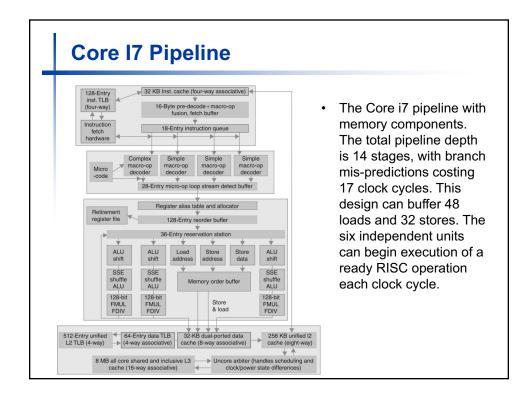

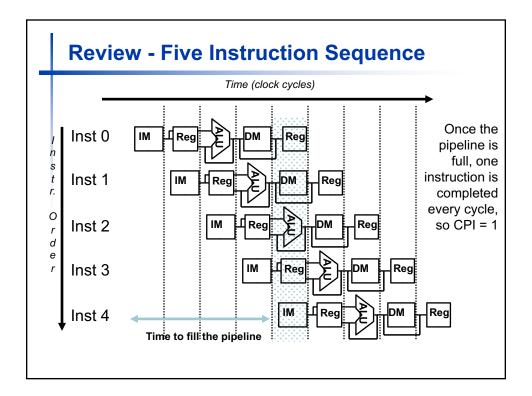

- All modern day processors use pipelining for performance (a CPI of 1 and a fast clock cycle).

- Pipeline clock rate limited by slowest pipeline stage so designing a balanced pipeline is important.

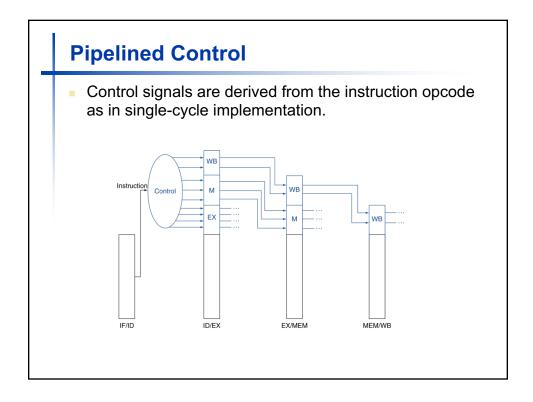

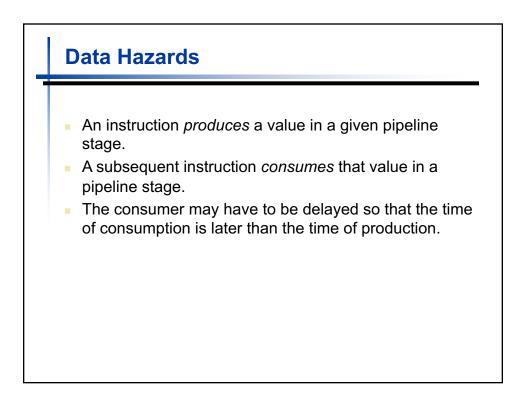

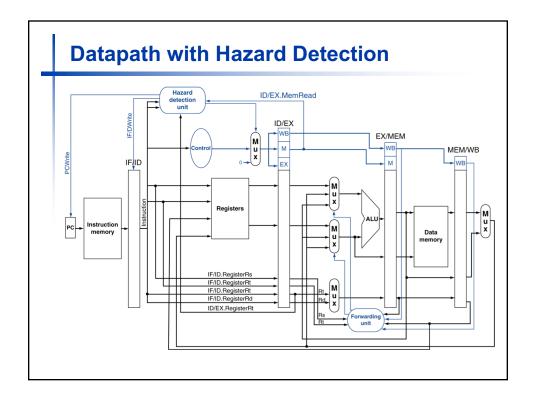

- Must detect and resolve hazards

- Structural hazards resolved by designing the pipeline correctly.

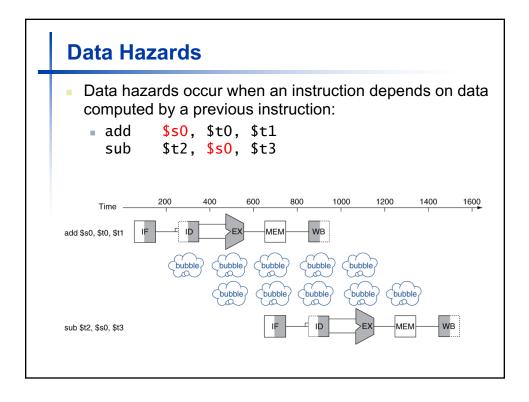

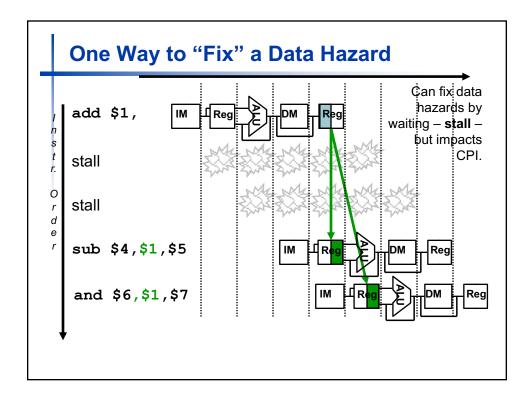

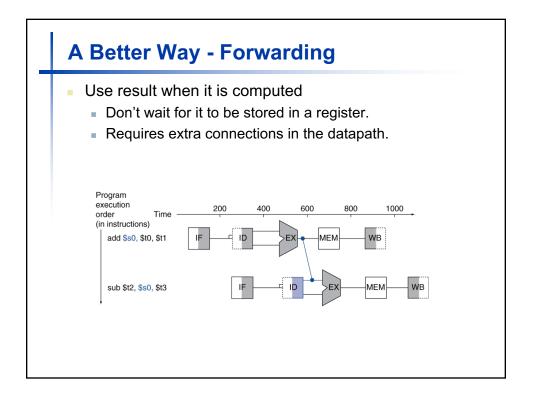

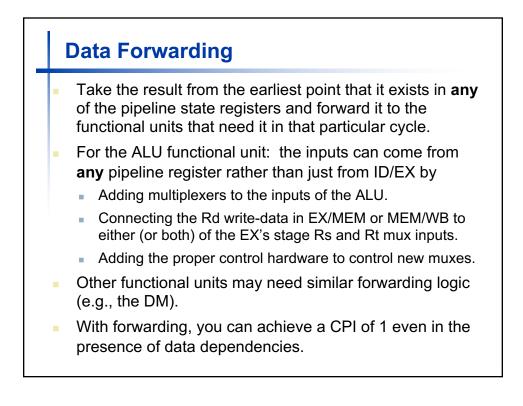

- Data hazards

- Stall (impacts CPI).

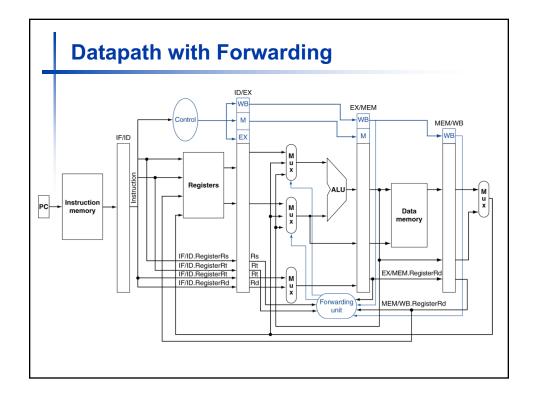

- Forward (requires hardware support).

- Control hazards put the branch decision hardware in as early a stage of the pipeline as possible

- Stall (impacts CPI).

- Delay decision (requires compiler support).

- Static and dynamic prediction (requires hardware support).